-

上海青浦物流倉(cāng)庫(kù)哪家服務(wù)好?吉新15000平倉(cāng)儲(chǔ)出租

-

吉新物流作為青浦倉(cāng)儲(chǔ)公司專(zhuān)業(yè)服務(wù)商提供哪些服務(wù)呢

-

關(guān)于吉新青浦倉(cāng)儲(chǔ)公司提供服務(wù),你想知道的都在這里

-

需求倉(cāng)庫(kù)托管代發(fā)貨的都選擇了這家上海倉(cāng)儲(chǔ)公司

-

上海倉(cāng)儲(chǔ)配送_吉新倉(cāng)庫(kù)面積租用靈活

-

上海倉(cāng)儲(chǔ)物流 吉新電商倉(cāng)庫(kù)火熱招租 消防自動(dòng)噴淋

-

上海倉(cāng)儲(chǔ)托管服務(wù)哪家好?吉新物流倉(cāng)儲(chǔ)配送服務(wù)

-

上海青浦倉(cāng)儲(chǔ)公司 吉新物流承接各種倉(cāng)庫(kù)托管代發(fā)貨

-

上海倉(cāng)儲(chǔ)公司 吉新提供物流倉(cāng)庫(kù)外包服務(wù)

-

上海青浦倉(cāng)庫(kù)出租 吉新物流倉(cāng)儲(chǔ)招租 100平起租

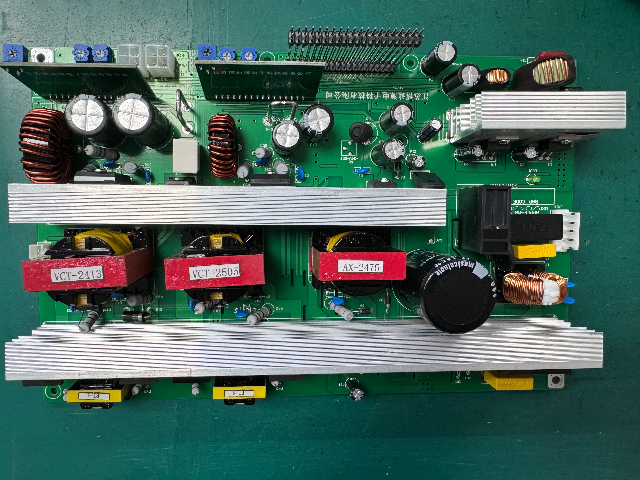

內(nèi)蒙古電力設(shè)備硬件開(kāi)發(fā)平均價(jià)格

多功能數(shù)據(jù)采集器硬件設(shè)計(jì)技巧——控制單元與優(yōu)化在多功能數(shù)據(jù)采集器的硬件設(shè)計(jì)中,控制單元的選擇與優(yōu)化是至關(guān)重要的一步。傳統(tǒng)設(shè)計(jì)中,我們常以ATmega8單片機(jī)為基礎(chǔ)構(gòu)建控制電路,但隨著技術(shù)的發(fā)展,更高性能的微處理器如ATmega16或STM32系列已成為主流選擇。這些微處理器不僅具備更高的運(yùn)算速度和更低的功耗,還提供了豐富的外設(shè)接口,如SPI、I2C等,便于擴(kuò)展和集成其他功能模塊。優(yōu)化技巧:選擇合適的微處理器:根據(jù)數(shù)據(jù)采集器的具體需求,如采集精度、處理速度、功耗等,選擇合適的微處理器。同時(shí),考慮其內(nèi)部資源和外部接口是否滿足設(shè)計(jì)要求。優(yōu)化電路設(shè)計(jì):在電路設(shè)計(jì)過(guò)程中,盡量減少不必要的元件和走線,降低電路復(fù)雜度,提高系統(tǒng)的穩(wěn)定性和可靠性。同時(shí),采用合理的布局和布線策略,減少信號(hào)干擾和噪聲。電源管理:合理設(shè)計(jì)電源管理電路,確保各功能模塊在正常工作狀態(tài)下獲得穩(wěn)定的電源供應(yīng)。同時(shí),考慮低功耗設(shè)計(jì),如采用休眠模式、自動(dòng)斷電等功能,以延長(zhǎng)設(shè)備的使用壽命。 硬件工程師需要和各種崗位交互,因此豐富的知識(shí)面、強(qiáng)大的協(xié)調(diào)能力必不可少。內(nèi)蒙古電力設(shè)備硬件開(kāi)發(fā)平均價(jià)格

硬件開(kāi)發(fā)

多功能數(shù)據(jù)采集器硬件設(shè)計(jì)技巧——通信與隔離技術(shù)在多功能數(shù)據(jù)采集器的硬件設(shè)計(jì)中,通信與隔離技術(shù)也是不可忽視的重要環(huán)節(jié)。通信電路的設(shè)計(jì)應(yīng)確保數(shù)據(jù)采集器與上位機(jī)或其他設(shè)備之間的數(shù)據(jù)傳輸穩(wěn)定可靠;而隔離技術(shù)的應(yīng)用則可以降低電路間的干擾和噪聲,提高系統(tǒng)的整體性能。設(shè)計(jì)技巧:通信電路設(shè)計(jì):根據(jù)實(shí)際需求選擇合適的通信協(xié)議和接口,如RS-232、RS-485、CAN總線等。在設(shè)計(jì)中,應(yīng)確保通信電路的抗干擾能力強(qiáng)、傳輸速度快、通信距離遠(yuǎn)。同時(shí),考慮通信數(shù)據(jù)的校驗(yàn)和糾錯(cuò)機(jī)制,以提高數(shù)據(jù)傳輸?shù)目煽啃浴8綦x技術(shù)應(yīng)用:在數(shù)據(jù)采集器的設(shè)計(jì)中,采用隔離技術(shù)可以降低電路間的干擾和噪聲。例如,在指令信號(hào)的傳輸中,可以使用數(shù)字隔離芯片進(jìn)行隔離處理;在模擬信號(hào)的傳輸中,可以采用變壓器或光耦等隔離器件進(jìn)行隔離。這些措施可以降低環(huán)路噪聲和共模干擾的影響,提高系統(tǒng)的穩(wěn)定性和可靠性。接口擴(kuò)展與兼容性:在設(shè)計(jì)中,應(yīng)充分考慮數(shù)據(jù)采集器的接口擴(kuò)展性和兼容性。通過(guò)預(yù)留足夠的接口資源和采用標(biāo)準(zhǔn)的接口協(xié)議,可以方便地與其他設(shè)備進(jìn)行連接和通信。同時(shí),考慮不同型號(hào)和品牌的設(shè)備之間的兼容性問(wèn)題,以確保數(shù)據(jù)采集器能夠廣泛應(yīng)用于各種場(chǎng)合。 內(nèi)蒙古智能設(shè)備硬件開(kāi)發(fā)調(diào)試硬件開(kāi)發(fā)和軟件開(kāi)發(fā)如何做好的統(tǒng)籌和協(xié)調(diào)?

FPGA(Field-ProgrammableGateArray,現(xiàn)場(chǎng)可編程門(mén)陣列)硬件設(shè)計(jì)是一個(gè)復(fù)雜但高度靈活的過(guò)程,它允許工程師通過(guò)編程來(lái)配置FPGA芯片以實(shí)現(xiàn)特定的數(shù)字電路功能。以下是對(duì)FPGA硬件設(shè)計(jì)流程的詳細(xì)解析:一、FPGA硬件設(shè)計(jì)流程概述FPGA硬件設(shè)計(jì)流程主要包括以下幾個(gè)關(guān)鍵步驟:需求分析、FPGA芯片選擇、硬件框圖設(shè)計(jì)、HDL編程、仿真測(cè)試、布局布線、配置與調(diào)試。二、具體步驟詳解需求分析確定FPGA的應(yīng)用需求,包括功能需求、性能需求、成本預(yù)算等。根據(jù)需求確定FPGA板卡的尺寸、工作頻率、IO口數(shù)量、運(yùn)行環(huán)境等設(shè)計(jì)規(guī)格。三、FPGA硬件設(shè)計(jì)工具在FPGA硬件設(shè)計(jì)過(guò)程中,需要使用一系列工具來(lái)輔助完成各個(gè)步驟。這些工具通常包括:IDE(集成開(kāi)發(fā)環(huán)境):如Xilinx的Vivado和Intel的QuartusPrime,它們集成了代碼編輯、綜合、仿真和調(diào)試等功能,能夠提高設(shè)計(jì)效率。HDL編輯器:用于編寫(xiě)和編輯HDL代碼。仿真工具:如ModelSim,用于對(duì)HDL代碼進(jìn)行功能仿真和時(shí)序仿真。布局布線工具:負(fù)責(zé)將HDL代碼翻譯成物理電路圖,并進(jìn)行布局和布線。四、FPGA硬件設(shè)計(jì)的優(yōu)勢(shì)FPGA硬件設(shè)計(jì)具有以下幾個(gè)優(yōu)勢(shì):靈活性:FPGA可以通過(guò)編程來(lái)配置不同的電路功能,具有很高的靈活性。

FPGA(現(xiàn)場(chǎng)可編程門(mén)陣列)設(shè)計(jì)常用的硬件描述語(yǔ)言(HDL)主要包括以下幾種:(VHSICHardwareDescriptionLanguage)定義:VHDL是一種標(biāo)準(zhǔn)化的硬件描述語(yǔ)言,用于描述數(shù)字電路系統(tǒng)的結(jié)構(gòu)、行為和功能。特點(diǎn):強(qiáng)大的抽象描述能力,有助于設(shè)計(jì)師從系統(tǒng)級(jí)開(kāi)始,逐步細(xì)化到邏輯級(jí)和電路級(jí)。語(yǔ)法嚴(yán)謹(jǐn),可讀性強(qiáng),使得設(shè)計(jì)過(guò)程更加規(guī)范和易于維護(hù)。:Verilog是另一種硬件描述語(yǔ)言,通過(guò)文本形式描述數(shù)字系統(tǒng)硬件的結(jié)構(gòu)和行為。特點(diǎn):語(yǔ)法類(lèi)似于C語(yǔ)言,學(xué)習(xí)成本相對(duì)較低,適合初學(xué)者和小型項(xiàng)目開(kāi)發(fā)。支持模塊化和層次化的設(shè)計(jì)方式,有助于降低設(shè)計(jì)的復(fù)雜性并提高設(shè)計(jì)的可重用性。提供了豐富的仿真和驗(yàn)證工具,便于在實(shí)際編程之前對(duì)設(shè)計(jì)進(jìn)行充分的測(cè)試和驗(yàn)證。SystemVerilog是Verilog的擴(kuò)展和增強(qiáng)版,增加了許多新的特性和功能。特點(diǎn):增加了面向?qū)ο缶幊痰奶匦裕珙?lèi)、接口、繼承等,提高了代碼的可重用性和可維護(hù)性。 硬件設(shè)計(jì)的細(xì)節(jié)決定產(chǎn)品的成功。

硬件開(kāi)發(fā)團(tuán)隊(duì)建設(shè)與資源籌備標(biāo)題:構(gòu)建硬件開(kāi)發(fā)團(tuán)隊(duì):團(tuán)隊(duì)建設(shè)與資源籌備策略?xún)?nèi)容概要:硬件開(kāi)發(fā)是一個(gè)復(fù)雜而多領(lǐng)域協(xié)作的過(guò)程,構(gòu)建一個(gè)團(tuán)隊(duì)至關(guān)重要。本文首先探討了如何根據(jù)項(xiàng)目需求組建團(tuán)隊(duì),包括確定團(tuán)隊(duì)規(guī)模、角色分配、技能要求等。隨后,詳細(xì)闡述了資源籌備的重要性,包括開(kāi)發(fā)工具(如EDA軟件、測(cè)試設(shè)備)、物料采購(gòu)、等方面。此外,還討論了團(tuán)隊(duì)溝通與協(xié)作機(jī)制,確保團(tuán)隊(duì)成員之間能夠配合,共同推進(jìn)項(xiàng)目進(jìn)展。關(guān)鍵點(diǎn):團(tuán)隊(duì)組建的原則與策略角色分配與技能要求資源籌備的具體步驟與注意事項(xiàng)團(tuán)隊(duì)溝通與協(xié)作機(jī)制建立。 datasheet就是電子元器件的數(shù)據(jù)手冊(cè),也叫規(guī)格書(shū)-SPEC。是硬件工程師常查閱的文檔之一。北京電力設(shè)備硬件開(kāi)發(fā)應(yīng)用

硬件開(kāi)發(fā)的首先是將用戶需求進(jìn)行分解,了解用戶需求,才能開(kāi)展關(guān)鍵器件選型、方案設(shè)計(jì)工作。內(nèi)蒙古電力設(shè)備硬件開(kāi)發(fā)平均價(jià)格

硬件設(shè)計(jì)的復(fù)雜性標(biāo)題:硬件開(kāi)發(fā)的復(fù)雜性挑戰(zhàn)在硬件開(kāi)發(fā)的領(lǐng)域,設(shè)計(jì)的復(fù)雜性是開(kāi)發(fā)者經(jīng)常面臨的一大難點(diǎn)。隨著技術(shù)的不斷進(jìn)步,現(xiàn)代硬件設(shè)備往往集成了大量的功能模塊,包括處理器、內(nèi)存、存儲(chǔ)設(shè)備、通信接口以及各類(lèi)傳感器等。這些模塊之間的互操作性、信號(hào)完整性、功耗管理以及電磁兼容性等問(wèn)題,都需要開(kāi)發(fā)者在設(shè)計(jì)階段就進(jìn)行周密的考慮和規(guī)劃。首先,模塊之間的互操作性要求開(kāi)發(fā)者對(duì)各個(gè)模塊的技術(shù)規(guī)格有深入的理解,以確保它們。能夠無(wú)縫地協(xié)同工作這涉及到大量的接口協(xié)議、時(shí)序要求以及數(shù)據(jù)傳輸速率的匹配等問(wèn)題。其次,信號(hào)完整性問(wèn)題也是硬件設(shè)計(jì)中的一個(gè)重要挑戰(zhàn)。高速信號(hào)在傳輸過(guò)程中容易受到干擾和衰減,導(dǎo)致信號(hào)質(zhì)量下降甚至丟失。因此,開(kāi)發(fā)者需要采用先進(jìn)的信號(hào)完整性仿真工具和方法,對(duì)設(shè)計(jì)進(jìn)行精確的分析和優(yōu)化。此外,功耗管理也是硬件設(shè)計(jì)中的一個(gè)重要方面。隨著能源問(wèn)題的日益突出,如何在保證設(shè)備性能的同時(shí)降低功耗,成為了開(kāi)發(fā)者必須面對(duì)的問(wèn)題。這要求開(kāi)發(fā)者在電路設(shè)計(jì)和軟件算法上進(jìn)行創(chuàng)新,以實(shí)現(xiàn)高效的能源利用。 內(nèi)蒙古電力設(shè)備硬件開(kāi)發(fā)平均價(jià)格

- 江蘇分析儀器設(shè)備硬件開(kāi)發(fā)需求 2024-12-19

- 福建風(fēng)力發(fā)電硬件開(kāi)發(fā)注意事項(xiàng) 2024-12-19

- 山東檢測(cè)儀器設(shè)備硬件開(kāi)發(fā)測(cè)試 2024-12-19

- 北京汽車(chē)新能源硬件開(kāi)發(fā)環(huán)境 2024-12-18

- 江西電子科技產(chǎn)品硬件開(kāi)發(fā)環(huán)境 2024-12-18

- 江西電子科技產(chǎn)品硬件開(kāi)發(fā)管理規(guī)范 2024-12-18

- 浙江儲(chǔ)能設(shè)備硬件開(kāi)發(fā)測(cè)試 2024-12-17

- 數(shù)據(jù)采集器硬件開(kāi)發(fā)應(yīng)用 2024-12-17

- 江西硬件開(kāi)發(fā)費(fèi)用 2024-12-17

- 內(nèi)蒙古檢測(cè)儀器設(shè)備硬件開(kāi)發(fā)分類(lèi) 2024-12-16

- 江西樣品全尺寸報(bào)告軟件有哪些 2024-12-27

- 嘉興直流電計(jì)量服務(wù) 2024-12-27

- 山東國(guó)產(chǎn)張力控制器價(jià)格 2024-12-27

- 小巧光纜巡線儀價(jià)格哪家便宜 2024-12-27

- 湖州電磁測(cè)量設(shè)備校準(zhǔn)費(fèi)用 2024-12-27

- 陜西通信共享洗衣機(jī)控制器 2024-12-27

- 浙江電梯測(cè)力傳感器制造廠家 2024-12-27

- 回路記錄儀生產(chǎn)廠家排行榜 2024-12-27

- 江西快速溫變高低溫試驗(yàn)箱哪個(gè)牌子好 2024-12-27

- 唐山進(jìn)口金相顯微鏡采購(gòu) 2024-12-27