-

科技之光,研發(fā)未來-特殊染色技術(shù)服務(wù)檢測中心

-

常規(guī)HE染色技術(shù)服務(wù)檢測中心:專業(yè)、高效-生物醫(yī)學(xué)

-

科研的基石與質(zhì)量的保障-動物模型復(fù)制實驗服務(wù)檢測中心

-

科技之光照亮生命奧秘-細胞熒光顯微鏡檢測服務(wù)檢測中心

-

揭秘微觀世界的窗口-細胞電鏡檢測服務(wù)檢測中心

-

科研的基石與創(chuàng)新的搖籃-細胞分子生物學(xué)實驗服務(wù)檢測中心

-

科研的堅實后盾-大小動物學(xué)實驗技術(shù)服務(wù)檢測中心

-

推動生命科學(xué)進步的基石-細胞生物學(xué)實驗技術(shù)服務(wù)

-

科技前沿的守護者-細胞藥效學(xué)實驗服務(wù)檢測中心

-

科研前沿的探索者-細胞遷移與侵襲實驗服務(wù)檢測中心

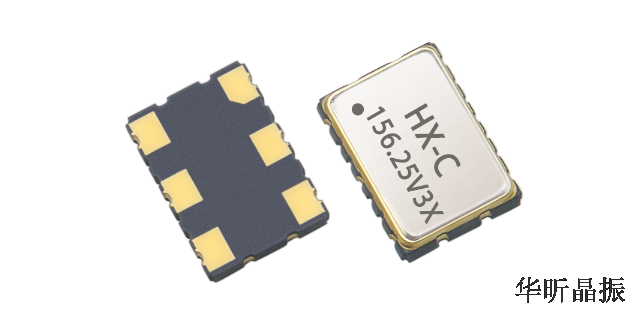

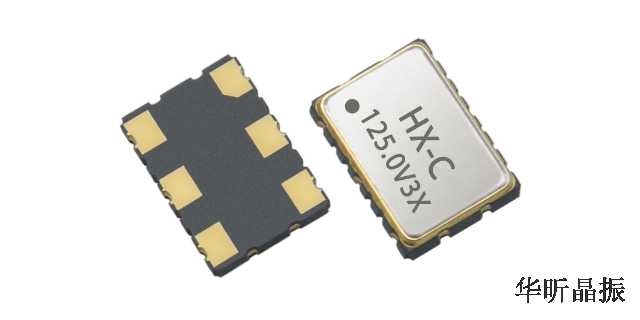

廣西差分晶振輸出模式

差分晶振的焊接溫度和時間控制是確保晶振性能穩(wěn)定和避免損壞的關(guān)鍵步驟。在焊接過程中,必須嚴格控制焊接溫度和焊接時間,以確保晶振的正常工作和延長其使用壽命。

首先,焊接溫度的控制至關(guān)重要。差分晶振的焊接溫度一般控制在220-250攝氏度之間。這個溫度范圍是為了保護晶振的內(nèi)部結(jié)構(gòu),避免高溫對晶振產(chǎn)生不良影響。如果溫度過高,可能會導(dǎo)致晶振內(nèi)部的結(jié)構(gòu)破壞,從而影響其性能。因此,在焊接過程中,務(wù)必使用合適的熱源,如熱風(fēng)槍或烙鐵,并確保溫度控制在適當(dāng)?shù)姆秶鷥?nèi)。

其次,焊接時間的控制同樣重要。焊接時間一般控制在2-5秒之間。過長的焊接時間可能會導(dǎo)致晶振的性能下降,甚至損壞晶振。因此,在焊接過程中,要快速而準確地完成焊接,避免過長時間的加熱。

此外,為了確保焊接質(zhì)量和避免晶振損壞,還需要注意以下幾點:

使用適當(dāng)?shù)暮稿a絲,通常選擇直徑為0.3mm至0.5mm的焊錫絲。

保持烙鐵頭的光滑,無鉤、無刺,以確保焊接過程中的良好接觸。

避免烙鐵頭重觸焊盤,不要反復(fù)長時間在一個焊盤上加熱,以免超過晶振的工作溫度范圍。

總之,差分晶振的焊接溫度和時間控制是確保晶振性能穩(wěn)定和避免損壞的關(guān)鍵。 差分晶振的抗振動能力如何?廣西差分晶振輸出模式

差分晶振與FPGA的連接方式及應(yīng)用

差分晶振以其獨特的差分信號輸出方式,有效地消除了共模噪聲,實現(xiàn)了高性能的系統(tǒng)運行。而FPGA,作為現(xiàn)場可編程門陣列,具備高度的靈活性和可配置性,使得其在各種應(yīng)用場景中都能發(fā)揮出色性能。那么,差分晶振如何與FPGA進行連接呢?

首先,差分晶振的輸出為差分信號,因此在與FPGA連接時,需要確保FPGA的輸入端口能夠接收差分信號。這通常意味著需要使用FPGA上的差分輸入接收器(DifferentialInputReceiver)來實現(xiàn)與差分晶振的連接。連接時,差分晶振的正負兩根信號線應(yīng)分別接入FPGA的差分輸入接收器的對應(yīng)引腳。這種連接方式可以有效地保證差分信號的完整性,避免因信號傳輸過程中的噪聲干擾而影響系統(tǒng)的性能。

在連接過程中,還需要注意差分晶振的工作電壓和頻率等參數(shù)與FPGA的兼容性。確保差分晶振的電源電壓、工作頻率等參數(shù)在FPGA的接受范圍內(nèi),以確保連接的穩(wěn)定性和可靠性。差分晶振與FPGA的連接,不僅使得系統(tǒng)能夠獲得穩(wěn)定、準確的時鐘信號,而且還可以通過FPGA的編程能力,實現(xiàn)對時鐘信號的靈活處理和控制。這使得差分晶振與FPGA的組合在各種需要高性能時鐘源的應(yīng)用場景中,如通信、數(shù)據(jù)處理等領(lǐng)域,具有廣泛的應(yīng)用前景。

深圳5032差分晶振差分晶振與數(shù)字電路之間的接口設(shè)計需要注意哪些問題?

差分晶振的自動相位控制(APC)功能解析

差分晶振獨特的差分結(jié)構(gòu)使其具有優(yōu)異的抗干擾能力和溫度穩(wěn)定性。然而,差分晶振的性能表現(xiàn),很大程度上取決于其自動相位控制(APC)功能的實現(xiàn)。自動相位控制(APC)是差分晶振的一項關(guān)鍵功能,它通過自動調(diào)整振蕩器的相位,保證輸出的穩(wěn)定性和準確性。APC功能的實現(xiàn),依賴于精密的電路設(shè)計和算法控制。在差分晶振工作過程中,APC功能能夠?qū)崟r監(jiān)測振蕩器的相位變化,一旦發(fā)現(xiàn)偏差,就會立即啟動調(diào)整機制,使振蕩器迅速恢復(fù)到正確的相位狀態(tài)。這種自動調(diào)整的能力,使得差分晶振在各種復(fù)雜的工作環(huán)境下,都能保持穩(wěn)定的輸出。無論是溫度變化、電源波動,還是外部干擾,APC功能都能有效地進行相位調(diào)整,確保差分晶振的性能不受影響。此外,APC功能還具有很高的響應(yīng)速度。一旦檢測到相位偏差,它能在極短的時間內(nèi)完成調(diào)整,保證差分晶振的輸出始終與設(shè)定值保持一致。這種快速響應(yīng)的特性,使得差分晶振在需要高精度、高穩(wěn)定性輸出的應(yīng)用中,具有不可替代的優(yōu)勢。

總的來說,差分晶振的自動相位控制(APC)功能是其性能穩(wěn)定、精度高的重要保障。它使差分晶振在各種工作環(huán)境下,都能保持穩(wěn)定的輸出,滿足各種高精度、高穩(wěn)定性要求的應(yīng)用需求。

差分晶振的同步能力如何?

差分晶振同步能力對整體系統(tǒng)的穩(wěn)定性和性能起著至關(guān)重要的作用。在深入探討差分晶振的同步能力時,我們首先要理解其工作原理和基本特性。差分晶振通過內(nèi)部的晶振電路產(chǎn)生穩(wěn)定的振蕩頻率,并通過差分輸出方式提供信號。這種差分輸出方式可以有效地抑制共模噪聲,提高信號的抗干擾能力。因此,差分晶振在復(fù)雜的電磁環(huán)境中也能保持較高的穩(wěn)定性,進而保證系統(tǒng)的同步精度。同步能力是差分晶振的一個重要指標。它決定了差分晶振在多個設(shè)備或系統(tǒng)之間能否實現(xiàn)精確的時間同步。在實際應(yīng)用中,差分晶振的同步能力受到多種因素的影響,包括環(huán)境溫度、電源電壓、負載變化等。然而,通過采用先進的溫度補償技術(shù)和電路設(shè)計,差分晶振能夠在各種環(huán)境下保持穩(wěn)定的振蕩頻率和出色的同步能力。此外,差分晶振的同步能力還與其輸出信號的相位噪聲和抖動性能密切相關(guān)。相位噪聲是衡量晶振輸出信號純凈度的重要指標,而抖動則反映了信號邊沿的穩(wěn)定性。差分晶振通過優(yōu)化電路設(shè)計和采用低噪聲元件,能夠有效地降低相位噪聲和抖動,從而進一步提高同步能力。總的來說,差分晶振具有出色的同步能力,能夠在各種復(fù)雜環(huán)境中保持穩(wěn)定的振蕩頻率和精確的時間同步。 差分晶振如何與FPGA連接?

差分晶振的抗沖擊能力探討差分晶振,作為一種高精度、高穩(wěn)定性的振蕩器,廣泛應(yīng)用于各種電子設(shè)備和系統(tǒng)中。在復(fù)雜多變的工作環(huán)境中,差分晶振的抗沖擊能力顯得尤為重要。那么,差分晶振的抗沖擊能力如何呢?首先,我們需要了解差分晶振的基本結(jié)構(gòu)和工作原理。差分晶振由石英晶體和振蕩電路組成,通過石英晶體的壓電效應(yīng)產(chǎn)生穩(wěn)定的振蕩信號。這種結(jié)構(gòu)決定了差分晶振具有較高的機械強度和抗震性能。其次,差分晶振在設(shè)計和制造過程中,會經(jīng)過嚴格的測試和篩選。例如,通過高低溫循環(huán)測試、沖擊測試等,確保產(chǎn)品在各種惡劣環(huán)境下仍能保持穩(wěn)定的性能。這些測試不僅提高了差分晶振的抗沖擊能力,還延長了其使用壽命。此外,差分晶振還采用了一些特殊的保護措施。例如,在晶振外殼內(nèi)部填充減震材料,減少外部沖擊對晶振的影響;在電路設(shè)計中加入濾波電路,降低電磁干擾對晶振穩(wěn)定性的影響。這些保護措施共同增強了差分晶振的抗沖擊能力。綜上所述,差分晶振具有較高的抗沖擊能力。通過合理的結(jié)構(gòu)設(shè)計、嚴格的測試和篩選以及特殊的保護措施,差分晶振能夠在各種惡劣環(huán)境下保持穩(wěn)定的性能。差分晶振的電磁兼容性如何?廣西差分晶振輸出模式

差分晶振的老化率如何?廣西差分晶振輸出模式

差分晶振的抗振動能力如何?差分晶振,作為一種高精度、高穩(wěn)定性的振蕩器,廣泛應(yīng)用于各類電子設(shè)備中,尤其是需要高精度時間基準和頻率源的領(lǐng)域。在各類應(yīng)用場景中,設(shè)備常常面臨各種振動環(huán)境,這對差分晶振的性能提出了較高的要求。差分晶振的抗振動能力主要取決于其內(nèi)部結(jié)構(gòu)和制造工藝。其設(shè)計通常采用防震、抗震的結(jié)構(gòu),如懸浮支撐、減震材料等,以降低外部振動對晶振的影響。同時,制造工藝的精細程度也直接影響其抗振動性能。在實際應(yīng)用中,差分晶振的抗振動能力往往通過嚴格的測試來驗證。常見的測試包括振動測試、沖擊測試等,以模擬設(shè)備在實際運行中所可能遇到的振動環(huán)境,從而評估差分晶振在這些環(huán)境下的性能表現(xiàn)。總的來說,差分晶振的抗振動能力較強,能夠滿足大多數(shù)應(yīng)用場景的需求。然而,不同的應(yīng)用場景對差分晶振的抗振動能力有不同的要求,因此在選擇差分晶振時,需要根據(jù)實際的應(yīng)用需求來選擇合適的型號和規(guī)格。此外,為了進一步提高差分晶振的抗振動能力,研發(fā)和生產(chǎn)過程中也在不斷探索新的技術(shù)和工藝。例如,采用新材料、新工藝來增強晶振的抗震性能,或者通過優(yōu)化電路設(shè)計來提高差分晶振在振動環(huán)境下的穩(wěn)定性。廣西差分晶振輸出模式

- 高精度無源晶振50MHZ 2024-12-25

- 3080無源晶振頻率 2024-12-24

- 杭州無源晶振分類 2024-12-24

- 高精度無源晶振價格 2024-12-23

- 汕頭工業(yè)級無源晶振 2024-12-23

- 貼片無源晶振 2024-12-22

- 貼片無源晶振品牌 2024-12-22

- 3225無源晶振生產(chǎn)廠家 2024-12-21

- 2520無源晶振負載電容 2024-12-21

- 耐高溫?zé)o源晶振22.1184MHZ 2024-12-20

- 浙江本地繼電器銷售 2024-12-25

- 杭州使用ABS電磁閥市場價 2024-12-25

- 中山光敏二極管現(xiàn)貨直發(fā) 2024-12-25

- 杭州室內(nèi)引導(dǎo)屏價格 2024-12-25

- DCS控制系統(tǒng)價位 2024-12-25

- 江蘇高頻高速SOCKET生產(chǎn)廠 2024-12-25

- 貴陽店用攝像頭哪種好 2024-12-25

- 濾波電容 2024-12-25

- 龍崗區(qū)儲能電容器 2024-12-25

- 東莞紫銅引線框架價格 2024-12-25