天津SIP封裝

通信SiP 在無線通信領域的應用較早,也是應用較為普遍的領域。在無線通訊領域,對于功能傳輸效率、噪聲、體積、重量以及成本等多方面要求越來越高,迫使無線通訊向低成本、便攜式、多功能和高性能等方向發展。SiP 是理想的解決方案,綜合了現有的芯核資源和半導體生產工藝的優勢,降低成本,縮短上市時間,同時克服了 SOC 中諸如工藝兼容、信號混合、噪聲干擾、電磁干擾等難度。手機中的射頻功放,集成了頻功放、功率控制及收發轉換開關等功能,完整地在 SiP 中得到了解決。SiP 在應用終端產品領域(智能手表、TWS、手機、穿戴式產品、智能汽車)的爆發點也將愈來愈近。天津SIP封裝

為了在 SiP 應用中得到一致的優異細間距印刷性能,錫膏的特性如錫粉尺寸、助焊劑系統、流變性、坍塌特性和鋼網壽命都很重要,都需要被仔細考慮。合適的鋼網技術、設計和厚度,配合印刷時使用好的板支撐系統對得到一致且優異的錫膏轉印效率也是很關鍵的。回流曲線需要針對不同錫膏的特性進行合適的設計來達到空洞較小化。從目前的01005元件縮小到008004,甚至于下一代封裝的0050025,錫膏的印刷性能變得非常關鍵。從使用 3 號粉或者 4 號粉的傳統表面貼裝錫膏印刷發展到更為復雜的使用 5、6 號粉甚至 7 號粉的 SiP 印刷工藝。新的工藝鋼網開孔更小且鋼網厚度更薄,對可接受的印刷錫膏體積的差異要求更為嚴格。除了必須要印刷更小和更薄的錫膏沉積,相鄰焊盤的間隙也更小了。有些廠家已經開始嘗試50 μm 的焊盤間隙。浙江芯片封裝型式SiP是理想的解決方案,綜合了現有的芯核資源和半導體生產工藝的優勢,降低成本,縮短上市時間。

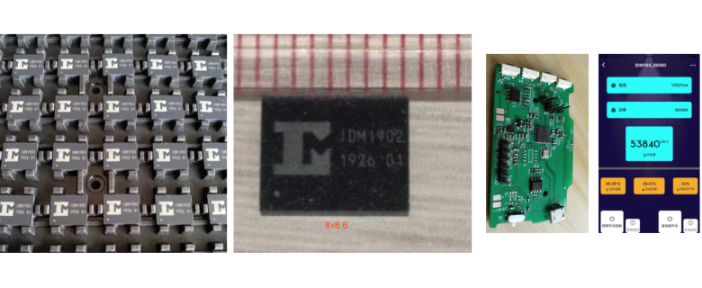

系統級封裝(SiP)是將多個集成電路(IC)和無源元件捆綁到單個封裝中,在單個封裝下它們協同工作的方法。這與片上系統(SoC)形成鮮明對比,功能則集成到同一個芯片中。將基于各種工藝節點(CMOS,SiGe,BiCMOS)的不同電路的硅芯片可以垂直或并排堆疊在襯底上。該封裝由內部接線進行連接,將所有芯片連接在一起形成一個功能系統。系統級封裝類似于片上系統(SOC),但它的集成度較低,并且使用的不是單一半導體制造工藝。常見的SiP解決方案可以利用多種封裝技術,例如倒裝芯片、引線鍵合、晶圓級封裝等。封裝在系統中的集成電路和其他組件的數量可變,理論上是無限的,因此,工程師基本上可以將整個系統集成到單個封裝中。

SiP模塊可靠度及失效分析,由于內部線路和基板之間的復雜鏈接,當模塊出現問題時,分析微米級組件的異常變得特別具有挑戰性,尤其是在電性測試期間,其他部件的導電性會影響測定結果。而且某些異常污染可能光只有幾奈米的厚度,如:氧化或微侵蝕,使用一般的光學或電子顯微鏡根本無法發現。為了將制程問題降至較低,云茂電子在SiP模塊失效分析領域持續強化分析能力,以X射線檢測(3D X–ray)、材料表面元素分析(XPS) 及傅立葉紅外線光譜儀(FTIR)等三大品管儀器找出解決之道。 汽車汽車電子是 SiP 的重要應用場景。

PoP(Package-on-Package),是用于將邏輯器件和存儲器器件進行疊層封裝的技術。通常情況下底層多為邏輯器件,例如移動電話基帶(調制解調器)處理器或應用處理器,上層為存儲器,例如閃存或者疊層內存芯片。顯然,這種垂直組合封裝的一個優點是節省了電路板空間。適用于需要在更小空間內實現更多功能的應用,例如數碼相機、PDA、MP3 播放器和移動游戲設備等。POP的工藝流程,PoP的組裝方式目前有兩種。一種是預制PoP工序,即先將PoP的多層封裝堆疊到一起,焊接成一個元器件,再貼裝到PCB上,然后再進行一次回流焊。一種是在板PoP工序上,依次將底部的BGA和頂部BGA封裝在PCB上,然后過一次回流焊。從某種程度上說:SIP=SOC+其他(未能被集成到SOC中的芯片和組件)。北京半導體芯片封裝技術

Sip系統級封裝通過將多個裸片(Die)和無源器件融合在單個封裝體內,實現了集成電路封裝的創新突破。天津SIP封裝

SMT生產工藝挑戰:元件小型化,Chip元件逐步淘汰,隨著產品集成化程度越來越高,產品小型化趨勢不可避免,因此0201元件在芯片級制造領域受到微型化發展趨勢,將被逐步淘汰。Chip元件普及,隨著蘋果i-watch的面世,SIP的空間設計受到挑戰,伴隨蘋果,三星等移動設備的高標要求,01005 chip元件開始普遍應用在芯片級制造領域。Chip元件開始推廣,SIP工藝的發展,要求元件板身必須小型化,隨著集成的功能越來越多,PCB承載的功能將逐步轉移到SIP芯片上,這就要求SIP在滿足功能的前提下,還能降尺寸控制在合理范圍,由此催生出0201元件的推廣與應用。天津SIP封裝

- 廣西半導體WMS系統市價 2024-12-26

- 中國臺灣定制測試數據分析和map處理系統售后服務 2024-12-25

- 安徽定制測試數據分析和map處理系統預算 2024-12-25

- 重慶定制測試數據分析和map處理系統平臺 2024-12-24

- 湖南哪里有測試數據分析和map處理系統預算 2024-12-24

- 湖南測試數據分析和map處理系統預算 2024-12-23

- 重慶哪里有測試數據分析和map處理系統性價比 2024-12-23

- 中國香港測試數據分析和map處理系統聯系方式 2024-12-22

- 山東哪里有測試數據分析和map處理系統 2024-12-22

- 定制測試數據分析和map處理系統包括哪些 2024-12-21

- 上海DC110V轉DC110V穩壓電源價格 2024-12-26

- 東莞epcos貼片繞線電感 2024-12-26

- 江蘇壓力傳感器哪家好 2024-12-26

- 宣城交流接觸器控制線束供應商 2024-12-26

- 羅湖區定制穩壓電路供應 2024-12-26

- 天津大規模快恢復二極管 2024-12-26

- 天津接插件價格 2024-12-26

- 廣東戶外LED異形屏供應商 2024-12-26

- 湖北防靜電硬化涂液 2024-12-26

- 開爾文結構分流電阻生產商推薦 2024-12-26