山東SIP封裝技術

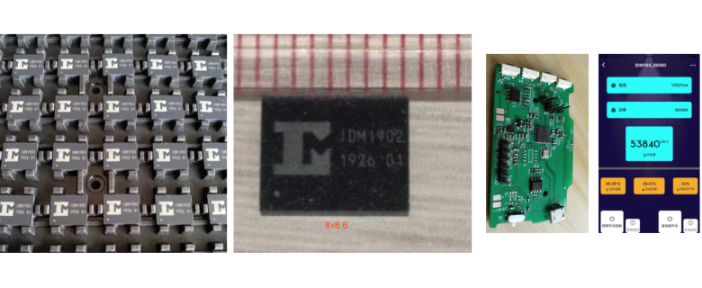

系統集成封裝(System in Package)可將多個集成電路 (IC) 和元器件組合到單個系統或模塊化系統中,以實現更高的性能,功能和處理速度,同時大幅降低電子器件內部的空間要求。SiP的基本定義,SiP封裝(System In Package系統級封裝)是將多種功能芯片,包括處理器、存儲器等功能芯片集成在一個封裝內,從而實現一個基本完整的功能,與SOC(System On Chip系統級芯片)相對應。不同的是SiP是采用不同功能的芯片在基板上進行并排或疊構后組成功能系統后進行封裝。而SOC則是將所需的組件高度集成在一塊芯片上進行封裝。構成SiP技術的要素是封裝載體與組裝工藝。山東SIP封裝技術

SiP模塊可靠度及失效分析,由于內部線路和基板之間的復雜鏈接,當模塊出現問題時,分析微米級組件的異常變得特別具有挑戰性,尤其是在電性測試期間,其他部件的導電性會影響測定結果。而且某些異常污染可能光只有幾奈米的厚度,如:氧化或微侵蝕,使用一般的光學或電子顯微鏡根本無法發現。為了將制程問題降至較低,云茂電子在SiP模塊失效分析領域持續強化分析能力,以X射線檢測(3D X–ray)、材料表面元素分析(XPS) 及傅立葉紅外線光譜儀(FTIR)等三大品管儀器找出解決之道。 山東SIP封裝技術SiP封裝基板半導體芯片封裝基板是封裝測試環境的關鍵載體。

淺談系統級封裝(SiP)的優勢及失效分析,半導體組件隨著各種消費性通訊產品的需求提升而必須擁有更多功能,組件之間也需要系統整合。因應半導體制程技術發展瓶頸,系統單芯片(SoC)的開發效益開始降低,異質整合困難度也提高,成本和所需時間居高不下。此時,系統級封裝(SiP)的市場機會開始隨之而生。 采用系統級封裝(SiP)的優勢,SiP,USI 云茂電子一站式微小化解決方案,相較于SoC制程,采用系統級封裝(SiP)的較大優勢來自于可以根據功能和需求自由組合,為客戶提供彈性化設計。以較常見的智能型手機為例,常見的的功能模塊包括傳感器、Wi-Fi、BT/BLE、RF FEM、電源管理芯片…...等。而系統級封裝即是將這些單獨制造的芯片和組件共同整合成模塊,再從單一功能模塊整合成子系統,再將該系統安裝到手機系統PCB上。

sip封裝的優缺點,SIP封裝的優缺點如下:優點:結構簡單:SIP封裝的結構相對簡單,制造和組裝過程相對容易。成本低:SIP封裝的制造成本較低,適合大規模生產。可靠性高:SIP封裝具有較好的密封性能,可以免受環境影響,提高產品的可靠性。適應性強:SIP封裝適用于對性能要求不高且需要大批量生產的低成本電子產品。缺點:引腳間距限制:SIP封裝的引腳中心距通常為2.54mm,引腳數從2至23不等,這限制了其在一些高密度、高性能應用中的使用。不適用于高速傳輸:由于SIP封裝的引腳間距較大,不適合用于高速數據傳輸。散熱性能差:SIP封裝的散熱性能較差,可能不適用于高功耗的芯片。SiP系統級封裝為設備提供了更高的性能和更低的能耗,使電子產品在緊湊設計的同時仍能實現突出的功能。

SiP系統級封裝作為一種集成封裝技術,在滿足多種先進應用需求方面發揮著關鍵作用。以其更小、薄、輕和更多功能的競爭力,為芯片和器件整合提供了新的可能性,目前其主要應用領域為射頻/無線應用、移動通信、網絡設備、計算機和外設、數碼產品、圖像、生物和MEMS傳感器等。固晶貼片機(Die bonder),是封裝過程中的芯片貼裝(Die attach)的主要設備。隨著SiP系統級封裝、3D封裝等先進封裝的普及,對固晶機設備在性能方面提出了更高的需求。隨著SiP模塊成本的降低,且制造工藝效率和成熟度的提高。陜西MEMS封裝廠商

SOC與SIP都是將一個包含邏輯組件、內存組件、甚至包含無源組件的系統,整合在一個單位中。山東SIP封裝技術

3D SIP。3D封裝和2.5D封裝的主要區別在于:2.5D封裝是在Interposer上進行布線和打孔,而3D封裝是直接在芯片上打孔和布線,電氣連接上下層芯片。3D集成目前在很大程度上特指通過3D TSV的集成。物理結構:所有芯片及無源器件都位于XY平面之上且芯片相互疊合,XY平面之上設有貫穿芯片的TSV,XY平面之下設有基板布線及過孔。電氣連接:芯片采用TSV與RDL直接電連接。3D集成多適用于同類型芯片堆疊,將若干同類型芯片豎直疊放,并由貫穿芯片疊放的TSV相互連接而成,見下圖。類似的芯片集成多用于存儲器集成,如DRAM Stack和FLASH Stack。山東SIP封裝技術

- 中國臺灣定制測試數據分析和map處理系統售后服務 2024-12-25

- 安徽定制測試數據分析和map處理系統預算 2024-12-25

- 重慶定制測試數據分析和map處理系統平臺 2024-12-24

- 湖南哪里有測試數據分析和map處理系統預算 2024-12-24

- 湖南測試數據分析和map處理系統預算 2024-12-23

- 重慶哪里有測試數據分析和map處理系統性價比 2024-12-23

- 中國香港測試數據分析和map處理系統聯系方式 2024-12-22

- 山東哪里有測試數據分析和map處理系統 2024-12-22

- 定制測試數據分析和map處理系統包括哪些 2024-12-21

- 河南測試數據分析和map處理系統哪家好 2024-12-21

- 廣州百兆網絡直通頭廠商有哪些 2024-12-26

- 江蘇合金精密電阻 2024-12-26

- HRS/廣瀨RM21WTP-CP10(71) 2024-12-26

- 宣城ACDC電源線束生產廠家 2024-12-26

- CDA12X10小金井FR302-02-F1 2024-12-26

- 180-4E2-83-PSL/DC24VKOGANEIHGA010LE1-PS/DC24V 2024-12-26

- TAC機械閥小金井250A2 2024-12-26

- 高柔韌性疊層無序納米銀網MDSN品牌 2024-12-26

- 龍崗區P溝道穩壓電路推薦 2024-12-26

- HRS/廣瀨FX20-100P-0.5SV15(10) 2024-12-26